(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

# 3.3.1 Number of research papers published per teacher in the Journals notified on UGC CARE list during the years (2022-23)

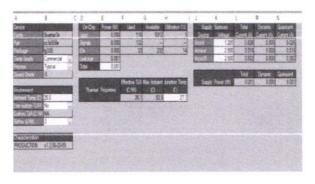

|           |                                                                                         |                                                                                              |                                                                                        |                                                                                        |                                                                                              | T                                                                                      | T                                                                                      | 1                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 7                                                                                       | 6                                                                                            | ъ                                                                                      | 4                                                                                      | ω                                                                                            | 2                                                                                      | ъ                                                                                      | S.No                                                                                                                                                                                              |

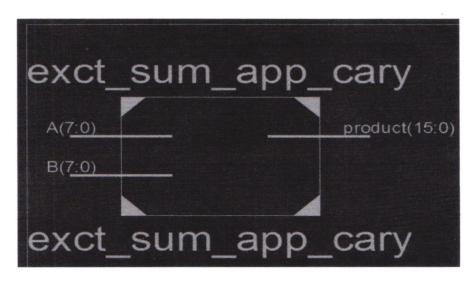

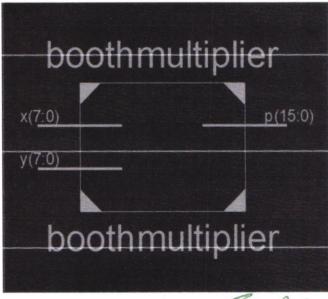

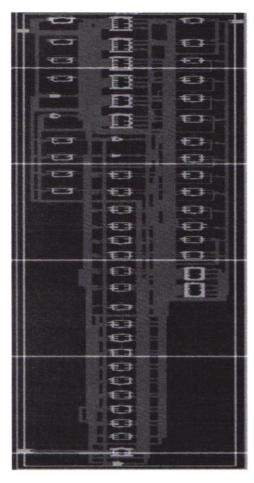

|           | Deign Of Multi Data Functional Based Fipflop For High-Speed Data Communication System   | Improvement Of Memory Data Corrections By Using CRC Technique For Fault Torrent Applications | Design Of High-Speed<br>Area Efficient Mac Unit<br>Using Reversible Logic              | Design Of High Order<br>Compression Multiplier<br>For High-Speed DSP<br>Applications   | Design Of Power Efficient 12T Sram Using Adiabatic Technique For Charge Recovery Application | Implementation Of Cryptography Using Rom Sub Modules And Exclusion Of Shift Rows       | Implementation Of Turbo Decoder For Completing Communication System In IVS             | Title of paper                                                                                                                                                                                    |

|           | Mr.D Suryaprakesh                                                                       | Mr.B Dasharadha                                                                              | Mr.V Guravaiah                                                                         | Mr.E Nagesh                                                                            | Mr.G Srinivas                                                                                | Mr.G Srinivas                                                                          | Dr.S. Kishore Reddy                                                                    | Name of the author/s                                                                                                                                                                              |

|           | ECE                                                                                     | ECE                                                                                          | ECE                                                                                    | ECE                                                                                    | ECE                                                                                          | ECE                                                                                    | ECE                                                                                    | Departm<br>ent of the<br>teacher                                                                                                                                                                  |

|           | International Journal of<br>Engineering Innovations in<br>Advanced Technology           | International Journal of<br>Engineering Innovations in<br>Advanced Technology                | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology                | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | Name of journal                                                                                                                                                                                   |

|           | 2022-23                                                                                 | 2022-23                                                                                      | 2022-23                                                                                | 2022-23                                                                                | 2022-23                                                                                      | Dec-22                                                                                 | 2022-23                                                                                | Calendar<br>Year of<br>publicati                                                                                                                                                                  |

|           | 2582-1431                                                                               | 2582-1431                                                                                    | 2582-1431                                                                              | 2582-1431                                                                              | 2582-1431                                                                                    | 2582-1431                                                                              | 2582-1431                                                                              | ISSN number                                                                                                                                                                                       |

|           | https://www.ijeiat.co<br>m/images/sliders/c1e5<br>4908047176d5d1111b<br>be0618d4997.ndf | https://www.ijeiat.co<br>m/images/sliders/8a4<br>b7adt2386f7d733f912<br>93cbc1e701.pdf       | https://www.ijeiat.co<br>m/images/sliders/16d<br>a2de01af4a657d6e26<br>87390e41a9d.pdf | https://www.ijeiat.co<br>m/images/sliders/7b1<br>6b0bbce76748afcf36e<br>09601eb150.pdf | https://www.ijeiat.co<br>m/images/sliders/983<br>ee5cf84da147528889f<br>a827d21684.pdf       | https://www.ijeiat.co<br>m/images/sliders/2f39<br>8b5805cb6ea287e8d8<br>443233c0aa.pdf | https://www.ijeiat.co<br>m/images/sliders/8a3<br>b67e10c6fc691e1c02<br>89ca5ecfc57.pdf | Link to the recognit /Digital OI Link to website of the Journal                                                                                                                                   |

| PRINCIPAL | https://www.ijeiat.co<br>m/images/sliders/c1e<br>549094447705d1/1                       | https://www.ijeiat.co<br>m/images/sliders/8a4<br>b7adf2386f7d733f91<br>293cbc1e701.pdf       | https://www.ijeiat.co<br>m/images/sliders/16d<br>a2de01af4a657d6e26<br>87390e41a9d.pdf | https://www.ijeiat.co<br>m/images/sliders/7b1<br>6b0bbce76748afcf36<br>e09601eb150.pdf | https://www.ijeiat.co<br>m/images/sliders/983<br>ee5cf84da147528889<br>fa827d21684.ndf       | https://www.ijeiat.co<br>m/images/sliders/2f3<br>98b5805cb6ea287e8<br>d8443233c0aa.pdf | https://www.ijeiat.co<br>m/images/sliders/8a3<br>b67e10c6fc691e1c02<br>89ca5ecfc57.pdf | Link to the recognition in UGC enlistment of the Journal  /Digital Object Identifier (doi) number  It is listed in  Link to article / baper / abstract  the Journal of the article Other, mention |

|           | UGC care                                                                                | UGC care                                                                                     | UGC care                                                                               | UGC care                                                                               | UGC care                                                                                     | UGC care                                                                               | UGC care                                                                               | nt of the Journal number It is listed in UGC care list / Scopus / Web of Science / Other, mention                                                                                                 |

Avanthi Institute of Engineering and Technology Gunthapally (V), Abdullapurmet (Mdl), R.R. Dist. Avanthi Institute of Engg. & Tooh

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512. <a href="https://www.aietg.ac.in">www.aietg.ac.in</a> email: <a href="mailto:principal.avanthi@gmail.com">principal.avanthi@gmail.com</a>

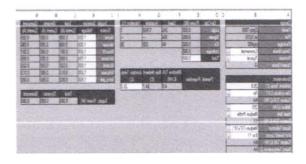

| 16                                                                                     | 15                                                                                                    | 14                                                                                     | 13                                                                                                     | 12                                                                                         | 11                                                                                              | 10                                                                                      | 9                                                                                      | ∞                                                                                      |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

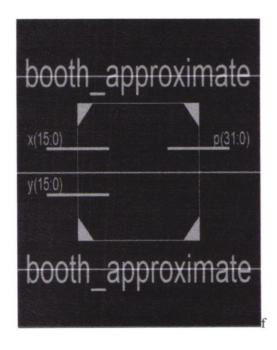

| Design Of High Order Compression Multiplier For High-Speed DSP Applications            | Design Of Power Efficient<br>12T Sram Using Adiabatic<br>Technique For Charge<br>Recovery Application | Implementation Of Cryptography Using Rom Sub Modules And Exclusion Of Shift Rows       | An Advanced VLSI Architecture For A Three- Operand binary adder for both high speed and area efficient | Design Of Compression Tree Based Wallace tree multiplifier for high speed VLSI application | The Design of Low-Power And High-Speed Full Adder through the exploration of novel XOR and XNOR | Implementation of SRAM Based Error Correction and Detection in Memory System Using LFSR | Design of Power and Area<br>Efficient Approximate<br>Multipliers                       | Efficient Design for Fixed-<br>Width Adder-Tree                                        |

| Dr.S. Kishore Reddy                                                                    | Dr.S. Kishore Reddy                                                                                   | Dr.S. Kishore Reddy                                                                    | Mr.P.Vijnatha Raju                                                                                     | Mr.G Srinivas                                                                              | Mr.V.Nagaraju                                                                                   | Mr.V.Nagaraju                                                                           | Dr.S. Kishore Reddy                                                                    | Mr.P.Vijnatha Raju                                                                     |

| ECE                                                                                    | ECE                                                                                                   | ECE                                                                                    | ECE                                                                                                    | ECE                                                                                        | ECE                                                                                             | ECE                                                                                     | ECE                                                                                    | ECE                                                                                    |

| International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology                         | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | Industrial Engineering<br>Journal                                                                      | Industrial Engineering<br>Journal                                                          | Industrial Engineering<br>Journal                                                               | International Journal of<br>Engineering Innovations in<br>Advanced Technology           | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology          |

| 2022-23                                                                                | 2022-23                                                                                               | 2022-23                                                                                | 2022-23                                                                                                | 2022-23                                                                                    | 2022-23                                                                                         | 2022-23                                                                                 | 2022-23                                                                                | 2022-23                                                                                |

| 2582-1431                                                                              | 2582-1431                                                                                             | 2582-1431                                                                              | 0970-2555                                                                                              | 0970-2555                                                                                  | 0970-2555                                                                                       | 2582-1431                                                                               | 2582-1431                                                                              | 2582-1431                                                                              |

| https://www.ijeiat.co<br>m/images/sliders/7b1<br>6b0bbce76748afcf36e<br>09601eb150.pdf | https://www.ijeiat.co<br>m/images/sliders/983<br>ee5cf84da147528889f<br>a827d21684.pdf                | https://www.ijeiat.co<br>m/images/sliders/2f39<br>8b5805cb6ea287e8d8<br>443233c0aa.pdf | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>59_online.pdf                                  | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>60_online.pdf                      | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>61_online.pdf                           | https://www.ijeiat.co<br>m/downloads/view/5/                                            | https://www.ijeiat.co<br>m/images/sliders/1bb<br>6264d69c7d8eb5fd88<br>51286ebfc3f.pdf | https://www.ijeiat.co<br>m/images/sliders/7f25<br>1919893764d45daea8<br>930dca9c95.pdf |

| https://www.jeiat.co<br>m/images/sliders/7b1<br>6b0bbce76748afc136<br>e09601ebf 14.7dd | https://www.ijeiat.co<br>m/images/sliders/983<br>ee5cf84da147528889<br>fa827d21684.pdf                | https://www.ijeiat.co<br>m/images/sliders/2f3<br>98b5805cb6ea287e8<br>d8443233c0aa.pdf | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>59_online.pdf                                  | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>60_online.pdf                      | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>61_online.pdf                           | https://www.ijeiat.co<br>m/downloads/view/5                                             | https://www.ijeiat.co<br>m/images/sliders/1bb<br>6264d69c7d8eb5fd8<br>851286ebfc3f.pdf | https://www.ijeiat.co<br>m/images/sliders/7t2<br>51919893764d45dae<br>a8930dca9c95.pdf |

| UGC care                                                                               | UGC care                                                                                              | UGC care                                                                               | UGC care                                                                                               | UGC care                                                                                   | UGC care                                                                                        | UGC care                                                                                | UGC care                                                                               | UGC care                                                                               |

Avanthi Institute of Engineering and Technology Gunthapally (V), Abdullapurmet (Mdl), R.R. Dist.

Avanthi Institute of Engg. & Tech

y Gunthapally (V), Abdullapurmet (Mdl), R.R. Dist.

(Approved by AICTE, Recg. By Govt. of T.S. & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

|                                         | 25                                                                                                          | 24                                                                                                     | 23                                                                                         | 22                                                                                              | 21                                                                                      | 20                                                                                     | 19                                                                                     | 18                                                                                           | 17                                                                                     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                         | Bidirectional Power Control Strategy for Super Capacitor Energy Storage System Based on MMC DC-DC Converter | An Advanced VLSI Architecture For A Three- Operand binary adder for both high speed and area efficient | Design Of Compression Tree Based Wallace tree multiplifier for high speed VLSI application | The Design of Low-Power And High-Speed Full Adder through the exploration of novel XOR and XNOR | Implementation of SRAM Based Error Correction and Detection in Memory System Using LFSR | Efficient Design for Fixed-<br>Width Adder-Tree                                        | Deign Of Multi Data Functional Based Fipflop For High-Speed Data Communication System  | Improvement Of Memory Data Corrections By Using CRC Technique For Fault Torrent Applications | Design Of High-Speed<br>Area Efficient Mac Unit<br>Using Reversible Logic              |

|                                         | Mr.M.SHANKAR                                                                                                | Dr.S. Kishore Reddy                                                                                    | Dr.S. Kishore Reddy                                                                        | Dr.S. Kishore Reddy                                                                             | Dr.S. Kishore Reddy                                                                     | Dr.S. Kishore Reddy                                                                    | Dr.S. Kishore Reddy                                                                    | Dr.S. Kishore Reddy                                                                          | Dr.S. Kishore Reddy                                                                    |

|                                         | EEE                                                                                                         | ECE                                                                                                    | ECE                                                                                        | ECE                                                                                             | ECE                                                                                     | ECE                                                                                    | ECE                                                                                    | ECE                                                                                          | ECE                                                                                    |

|                                         | The International journal of analytical and experimental modal analysis                                     | Industrial Engineering<br>Journal                                                                      | Industrial Engineering<br>Journal                                                          | Industrial Engineering<br>Journal                                                               | International Journal of<br>Engineering Innovations in<br>Advanced Technology           | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology          | International Journal of<br>Engineering Innovations in<br>Advanced Technology                | International Journal of<br>Engineering Innovations in<br>Advanced Technology          |

|                                         | 2022-23                                                                                                     | 2022-23                                                                                                | 2022-23                                                                                    | 2022-23                                                                                         | 2022-23                                                                                 | 2022-23                                                                                | 2022-23                                                                                | 2022-23                                                                                      | 2022-23                                                                                |

|                                         | 0886-9367                                                                                                   | 0970-2555                                                                                              | 0970-2555                                                                                  | 0970-2555                                                                                       | 2582-1431                                                                               | 2582-1431                                                                              | 2582-1431                                                                              | 2582-1431                                                                                    | 2582-1431                                                                              |

| 3 m m m m m m m m m m m m m m m m m m m | https://drive.google.com/file/d/1WsLOUbg<br>F9eeH3P2cE8.IG410p<br>VsXb8sTT/view                             | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>59_online.pdf                                  | http://www.journal-<br>iiie-<br>india.com/1 july 23/<br>60 online.pdf                      | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>61_online.pdf                           | https://www.ijeiat.co<br>m/images/sliders/d1f4<br>07a7dd80af0150ec20<br>70e063e2e0.ndf  | https://www.ijeiat.co<br>m/images/sliders/7f25<br>1919893764d45daea8<br>930dca9c95.pdf | https://www.ijeiat.co<br>m/images/sliders/c1e5<br>4908047176d5d111b<br>be0618d4997.pdf | https://www.ijeiat.co<br>m/images/sliders/8a4<br>b7adf2386f7d733f912<br>93cbc1e701.pdf       | https://www.ijeiat.co<br>m/images/sliders/16d<br>a2de01af4a657d6e26<br>87390e41a9d.pdf |

| PRINCIPAL                               | https://driegophe.com/file/full/syl/2006<br>gF9eeH3P2cE8JG41<br>OnVsXb8sTT/view                             | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>59_online.pdf                                  | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>60_online.pdf                      | http://www.journal-<br>iiie-<br>india.com/1_july_23/<br>61_online.pdf                           | https://www.ijeiat.co<br>m/images/sliders/d1f<br>407a7dd80af0150ec2<br>070e063e2e0.ndf  | https://www.ijeiat.co<br>m/images/sliders/7f2<br>51919893764d45dae<br>a8930dca9c95.pdf | https://www.ijeiat.co<br>m/images/sliders/c1e<br>54908047176d5d111<br>bbe0618d4997.pdf | https://www.ijeiat.co<br>m/images/sliders/8a4<br>b7adf2386f7d733f91<br>293cbc1e701.pdf       | https://www.ijeiat.co<br>m/images/sliders/16d<br>a2de01af4a657d6e26<br>87390e41a9d.pdf |

| 0                                       | UGC care                                                                                                    | UGC care                                                                                               | UGC care                                                                                   | UGC care                                                                                        | UGC care                                                                                | UGC care                                                                               | UGC care                                                                               | UGC care                                                                                     | UGC care                                                                               |

Avanthi Institute of Engg. & Tech.

Avanthi Institute of Engineering and Technology Gunthapally (V), Abdullapurmet (Mdl), R.R. Dist.

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

| 34                                                                                 | 33                                                    | 32                                                                           | 31                                                                | 30                                                           | 29                                                                                | 28                                                                                             | 27                                                                                 | 26                                                                                 |

|------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

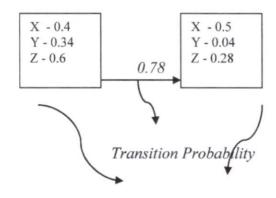

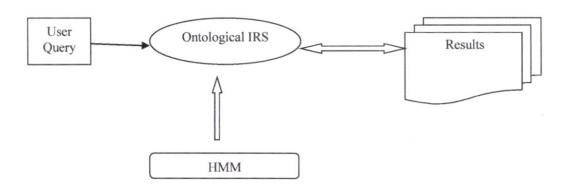

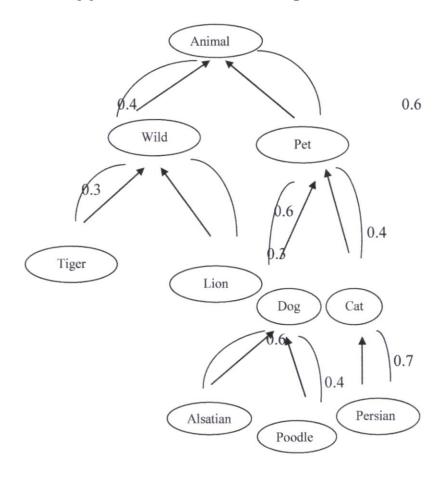

| FUZZY LOGIC CONTROLLER BASED DVR TO COMPENSATE VOLTAGE SAG AND SWELL WITH SRF      | Compensation Reward<br>Management                     | COMPENSATION<br>MANAGEMENT                                                   | SUCCESS OF SKILL<br>BASED PAY PLANS                               | CONCEPTUAL PAPER WORK ON PAY STRUCTURE                       | Optimized Robot Process Automated Path Navigation InTime Varying Networks         | An Improved Fast and<br>Secure CAMEL Based<br>Authenticated Key in<br>Smart Health Care System | Applying Hidden Markow<br>Models to Ontology Based<br>IRS for Coherence            | DESIGN AND SIMULATION OF MPC WITH FLC BASED HYBRID SYSTEM                          |

| Ms.M.RAGINI                                                                        | Dr.Y.JAYAPRADHA                                       | Dr.Y.JAYAPRADHA                                                              | Dr.Y.JAYAPRADHA                                                   | Dr.Y.JAYAPRADHA                                              | Dr.Shaik Shakeer<br>Basha                                                         | Dr. Shaik Shakeer<br>Basha                                                                     | Dr. SHAHEBAZ<br>AHMED KHAN                                                         | Mr.T.KRANTI<br>KUMAR                                                               |

| HER                                                                                | MBA                                                   | MBA                                                                          | MBA                                                               | MBA                                                          | CSE                                                                               | CSE                                                                                            | CSE                                                                                | EEE                                                                                |

| The International journal of analytical and experimental modal analysis            | WEBOLOGY                                              | International Journal of<br>Early Childhood Special<br>Education (INT-JECSE) | ShodhaSamhita: Journal of Fundamental & Comparative Research      | JOURNAL OF<br>MANAGEMENT AND<br>ENTREPRENEURSHIP             | Journal of Jilin University<br>(Engineering and<br>Technology Edition)            | UNIVERSAL WISER<br>PUBLISHER                                                                   | Journal of Information and<br>Computational Science                                | The International journal of analytical and experimental modal analysis            |

| 2022-23                                                                            | 2022-23                                               | 2022-23                                                                      | 2022-23                                                           | 2022-23                                                      | 2022-23                                                                           | 2022-23                                                                                        | 2022-23                                                                            | 2022-23                                                                            |

| 0886-9367                                                                          | 1735-188X                                             | 1308-5581                                                                    | 2277-7067                                                         | 2229-5348                                                    | 1671-5497                                                                         | http://ojs.wiserpu<br>b.com/index.php(<br>SCOPUS<br>INDEXED)                                   | 1548-7741                                                                          | 0886-9367                                                                          |

| https://drive.google.c<br>om/file/d/1CwPf5_u7<br>SNaTys4ty4oA-<br>ZH3CqvGHHIO/view | https://www.webolog<br>y.org/abstract.php?id<br>=4561 | https://www.int-<br>jecse.net/article/COM<br>PENSATION+MAN<br>AGEMENT 4972/  | https://kksushodhasa<br>mhita.org/index.php/s<br>dsa/issue/view/5 | https://xime.org/jme/p<br>hp/journal.php?booki<br>d=30type=0 | https://jilindaxuexueb<br>ao.net/details.php?id=<br>DOI:10.17605/OSF.I<br>O/WX4CV | https://ojs.wiserpub.c<br>om/index.php/CCDS/<br>article/view/1423/972                          | https://drive.google.c<br>om/file/d/1nZYyTTS<br>QMoEjKiuFzNjhfRn<br>2kD5E_me2/view | https://drive.google.c<br>om/file/d/11z0UucK1<br>Hx_m5nFVTSjcwQd<br>yo8ETEK0x/view |

| https://drive.google.com/file/d/1CwPf5_u 7SNaTys4ty4oA- ZH3CqvGHHIO/vie            | https://www.webolo<br>gy.org/abstract.php?i<br>d=4561 | https://www.int-<br>jecse.net/article/CO<br>MPENSATION+MA<br>NAGEMENT 4972/  | https://kksushodhasa<br>mhita.org/index.php/<br>sdsa/issue/view/5 | https://xime.org/jme/<br>php/journal.php?boo<br>kid=30type=0 | https://jilindaxuexue<br>bao.net/details.php?i<br>d=DOI:10.17605/OS<br>F.IO/WX4CV | https://ojs.wiserpub.c<br>om/index.php/CCDS<br>/article/view/1423/97                           | https://drive.google.c<br>om/file/d/1nZYyTTS<br>OMoEjKiuFzNjhfRn<br>2kD5E me2/view | https://drive.google.c<br>om/file/d/1Iz0UucKI<br>Hx_m5nFVTSjcwQd<br>yo8ETEK0x/view |

| UGC care                                                                           | WEBOLOGY                                              | SCOPUS                                                                       | UGC care                                                          | UGC care                                                     | SCOPUS                                                                            | SCOPUS                                                                                         | UGC care                                                                           | UGC care                                                                           |

PRINCIPAL

Avanthi Institute of Engineering and Technology (V), Abdullapurmet (Mdl), R.R. Dist.

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512. www.aietg.ac.in email: principal.avanthi@gmail.com

| 40                                                                                | 39                                                                                | 38                                                                                | 37                                                                                | 36                                                                                                   | 35                                                                                 |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

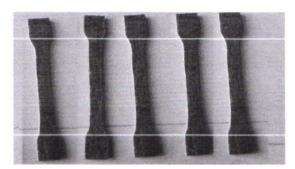

| EXPERIMENTATION AND ANALYSIS OF NATURAL FIBER REINFORCED POLYMER MATRIX COMPOSITE | EXPERIMENTATION AND ANALYSIS OF NATURAL FIBER REINFORCED POLYMER MATRIX COMPOSITE | EXPERIMENTATION AND ANALYSIS OF NATURAL FIBER REINFORCED POLYMER MATRIX COMPOSITE | EXPERIMENTATION AND ANALYSIS OF NATURAL FIBER REINFORCED POLYMER MATRIX COMPOSITE | A NOVEL PID CONTROLLER BASED D-STATCOM FOR ENHANCING POWER QUALITY WITH PR-FB CONTROLLER             | A NOVEL BI- DIRECTIONAL EV HYBRID ENERGY STORAGE FOR V2G SYSTEM                    |

| Mr.G Vinod Kumar                                                                  | Mr.Mallikanti<br>Venkateswarlu                                                    | Mr.Kolla Sumanth                                                                  | Dr Ramesh Babu<br>Yeluri                                                          | Mr.T.KRANTI<br>KUMAR                                                                                 | Mrs.E.PRASANNA                                                                     |

| MECH                                                                              | MECH                                                                              | МЕСН                                                                              | МЕСН                                                                              | EEE                                                                                                  | EEE                                                                                |

| International Journal of<br>Mechanical Engineering                                | Journal of Interdisciplinary<br>Cycle Research                                                       | Journal of Interdisciplinary<br>Cycle Research                                     |

| 2022-23                                                                           | 2022-23                                                                           | 2022-23                                                                           | 2022-23                                                                           | 2022-23                                                                                              | 2022-23                                                                            |

| 0974-5823                                                                         | 0974-5823                                                                         | 0974-5823                                                                         | 0974-5823                                                                         | 0022-1945                                                                                            | 0022-1945                                                                          |

| https://www.kalaharij<br>ournals.com/resource<br>s/MAY_198.pdf                    | https://www.kalaharij<br>ournals.com/resource<br>s/MAY_198.pdf                    | https://www.kalaharij<br>ournals.com/resource<br>s/MAY_198.pdf                    | https://www.kalaharij<br>ournals.com/resource<br>s/MAY_198.pdf                    | https://drive.google.com/file/d/1aXZH7ZC<br>om/file/d/1aXZH7ZC<br>00ZBiuL.VD2Twad<br>KBGD2gF1Xp/view | https://drive.google.c<br>om/file/d/12qPy3Nxd<br>y2sRhfHJFCW4rBL<br>M4-4z5T8w/view |

| https://www.kalahari<br>journals.com/resourc<br>es/MAY 198.pdf                    | https://www.kalahari<br>journals.com/resourc<br>es/MAY_198.pdf                    | https://www.kalahari<br>journals.com/resourc<br>es/MAY_198.pdf                    | https://www.kalahari<br>journals.com/resourc<br>es/MAY_198.pdf                    | https://drive.google.c<br>om/file/d/laXZH7Z<br>C00ZBiuLVD2Twad<br>KBGD2gF1Xp/vie                     | https://drive.google.com/file/d/12qPy3Nx<br>dy2sRhfHJFCW4rB<br>LM4-4z5T8w/view     |

| UGC care                                                                                             | UGC care                                                                           |

PRINCIPAL

Avanthi Institute of Engineering and Technologxunthapally (V), Abdullapurmet (Mdl), R.R. Dist. Avanthi Institute of Engg. & Tech

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

|   | 47                                                                  | 46                                                                      | 45                                                                     | 44                                                                     | 43                                                                                     | 42                                                                                     | 41                                                                                     |

|---|---------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

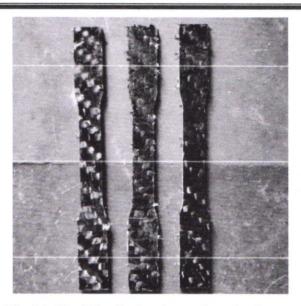

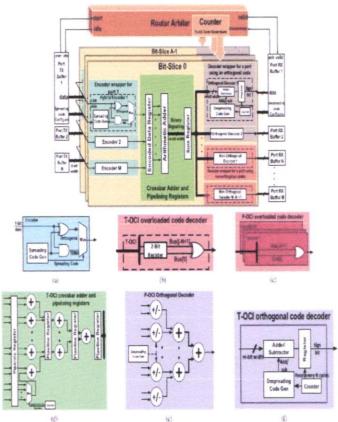

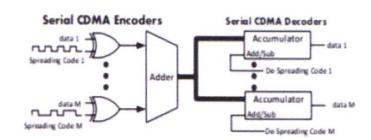

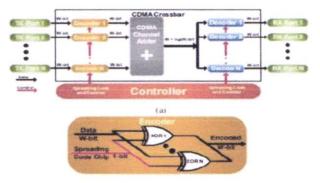

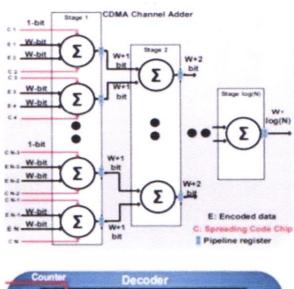

|   | OVERLOADED CDMA<br>CROSSBAR FOR<br>NETWORK-ON- CHIP                 | OVERLOADED CDMA<br>CROSSBAR FOR<br>NETWORK-ON- CHIP                     | 12T MEMORY CELLFORAEROSPACEA PPLICATIONS IN NANO SCALE CMOS TECHNOLOGY | 12T MEMORY CELLFORAEROSPACEA PPLICATIONS IN NANO SCALE CMOS TECHNOLOGY | INVESTIGATION AND CHARACTERIZATION OF GRAPHITE BASED CARBON REINFORCED LAMINATES       | INVESTIGATION AND CHARACTERIZATION OF GRAPHITE BASED CARBON REINFORCED LAMINATES       | INVESTIGATION AND CHARACTERIZATION OF GRAPHITE BASED CARBON REINFORCED LAMINATES       |

|   | Mr.D.SuryaPrakesh,                                                  | Dr.S. Kishore Reddy                                                     | Dr G Chandra Shekar                                                    | Dr.S. Kishore Reddy                                                    | Mr.G.VINOD<br>KUMAR                                                                    | Mr.Mallikanti<br>Venkateswarlu                                                         | Dr. RAMESH BABU<br>YELURI                                                              |

|   | ECE                                                                 | ECE                                                                     | ECE                                                                    | ECE                                                                    | MECH                                                                                   | МЕСН                                                                                   | MECH                                                                                   |

|   | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)   | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)       | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)      | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)      | International Journal of<br>Research in Engineering<br>and Applied<br>Sciences(IJREAS) | International Journal of<br>Research in Engineering<br>and Applied<br>Sciences(IJREAS) | International Journal of<br>Research in Engineering<br>and Applied<br>Sciences(IJREAS) |

|   | 2022-23                                                             | 2022-23                                                                 | 2022-23                                                                | 2022-23                                                                | 2022-23                                                                                | 2022-23                                                                                | 2022-23                                                                                |

|   | 0889-6402                                                           | 0889-6402                                                               | 0889-6402                                                              | 0889-6402                                                              | 2249-3905                                                                              | 2249-3905                                                                              | 2249-3905                                                                              |

| 8 | http://www.journalodi<br>.com/article_view.php<br>?id=50379&ctype=a | http://www.journalodj<br>.com/article_view.php<br>?id=50379&ctype=a     | http://www.journalodj<br>.com/article_view.php<br>?id=50380&ctype=a    | http://www.journalodj<br>.com/article_view.php<br>?id=50380&ctype=a    | https://euroasiapub.or<br>g/wp-<br>content/uploads/IJRE<br>A3SOct22-RamB.pdf           | https://euroasiapub.or<br>g/wp-<br>content/uploads/IJRE<br>A3SOct22-RamB.pdf           | https://euroasiapub.or<br>g/wp-<br>content/uploads/IJRE<br>A3SOct22-RamB.pdf           |

| 1 | http://www.journalodi.com/article_view.php?id=50379&dyp             | http://www.journalo<br>dj.com/article_view.<br>php?id=50379&ctyp<br>e=a | http://www.journalodj.com/article_view.php?id=50380&ctyp               | http://www.journalodj.com/article_view.php?id=50380&ctyp_e=a           | https://euroasiapub.o<br>rg/wp-<br>content/uploads/IJRE<br>A3SOct22-<br>RamB.pdf       | https://euroasiapub.o<br>rg/wp-<br>content/uploads/IJRE<br>A3SOct22-<br>RamB.pdf       | https://euroasiapub.o<br>rg/wp-<br>content/uploads/IJRE<br>A3SOct22-<br>RamB.pdf       |

|   | SCOPUS                                                              | SCOPUS                                                                  | SCOPUS                                                                 | SCOPUS                                                                 | UGC care                                                                               | UGC care                                                                               | UGC care                                                                               |

PRINCIPAL

Avanthi Institute of Engineering and Technology Avanthi Institute of Engg. & Teci

Gunthapally (V), Abdullapurmet (Mdl), R.R. Dist.

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

| ſ                                                                                                   | 1                                                                                            |                                                                                              | T                                                                                                |                                                                                                  |                                                                     | ,                                                                   |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| 54                                                                                                  | 53                                                                                           | 52                                                                                           | 51                                                                                               | 50                                                                                               | 49                                                                  | 48                                                                  |

| Mplementation Of Weighted Pseudorandom Test Pattern Generator for a Built In Self Test Architecture | Design And Implementation Of High Speed Low Power Mux Based Full Adder Using 16nm Technology | Design And Implementation Of High Speed Low Power Mux Based Full Adder Using 16nm Technology | Design And Implementation Of Low Power, Area And High Performance 4 Bit Sequence Digital Counter | Design And Implementation Of Low Power, Area And High Performance 4 Bit Sequence Digital Counter | VLSI DESIGN FOR CONVOLUTIVE BLIND SOURCE SEPARATION                 | VLSI DESIGN FOR<br>CONVOLUTIVE BLIND<br>SOURCE SEPARATION           |

| Dr.S.Kishore Reddy                                                                                  | Mr.P.Vijnatha Raju                                                                           | Dr.S.Kishore Reddy                                                                           | Mr.Vasantha Nagaraju                                                                             | Dr.S.Kishore Reddy                                                                               | Dr.Siddhartha Bangaru                                               | Dr.S.Kishore Reddy                                                  |

| ECE                                                                                                 | ECE                                                                                          | ECE                                                                                          | ECE                                                                                              | ECE                                                                                              | ECE                                                                 | ECE                                                                 |

| Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                                   | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                            | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                            | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                                | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                                | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)   | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)   |

| 2022-23                                                                                             | 2022-23                                                                                      | 2022-23                                                                                      | 2022-23                                                                                          | 2022-23                                                                                          | 2022-23                                                             | 2022-23                                                             |

| 0889-6402                                                                                           | 0889-6402                                                                                    | 0889-6402                                                                                    | 0889-6402                                                                                        | 0889-6402                                                                                        | 0889-6402                                                           | 0889-6402                                                           |

| http://www.journalodj<br>.com/article_view.php<br>?id=50393&ctype=a                                 | http://www.journalodj<br>.com/article_view.php<br>?id=50392&ctype=a                          | http://www.journalodj<br>.com/article_view.php<br>?id=50392&ctype=a                          | http://www.journalodj<br>.com/article_view.php<br>?id=50391&ctype=a                              | http://www.journalodj<br>.com/article_view.php<br>?id=50391&ctype=a                              | http://www.journalodj<br>.com/article_view.php<br>?id=50388&ctype=a | http://www.journalodj<br>.com/article_view.php<br>?id=50388&ctype=a |

| http://www.journalodj.com/article_view.php?id=50393&ctype==a                                        | http://www.journalodj.com/article_view.php?id=50392&ctyp                                     | http://www.journalodj.com/article_view.php?id=50392&ctyp                                     | http://www.journalodj.com/article_view.php?id=50391&ctyp_e=a                                     | http://www.journalodj.com/article_view.php?id=50391&ctyp_e=a                                     | http://www.journalodj.com/article_view.php?id=50388&ctyp_e=a        | http://www.journalodj.com/articleview.php?id=50388&ctype=a          |

| SCOPUS                                                                                              | SCOPUS                                                                                       | SCOPUS                                                                                       | SCOPUS                                                                                           | SCOPUS                                                                                           | SCOPUS                                                              | SCOPUS                                                              |

Sall

Avanthi Institute of Engineering and Technology

Avanthi Institute of Engg. & Tech.

Gunthanalis An Abdullapurmet (Mdl), R.R. Dist.

(Approved by AICTE, Recg. By Govt. of T.S & Affiliated to JNTUH, Hyderabad)

NAAC "B++" Accredited Institute

Gunthapally (V), Abdullapurmet(M), RR Dist, Near Ramoji Film City, Hyderabad -501512.

www.aietg.ac.in email: principal.avanthi@gmail.com

| 59                                                                              | 58                                                                              | 57                                                                                        | 56                                                                                        | 55                                                                                                  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| AN EFFICIENT VLSI ARCHITECTURE TO REMOVE IMPULSE NOISE IN IMAGES USING DECISION | AN EFFICIENT VLSI ARCHITECTURE TO REMOVE IMPULSE NOISE IN IMAGES USING DECISION | Rounding Based Approximate Multiplier For High Speed Yet Energy EfficientDSP Applications | Rounding Based Approximate Multiplier For High Speed Yet Energy EfficientDSP Applications | Mplementation Of Weighted Pseudorandom Test Pattern Generator for a Built In Self Test Architecture |

| Mr.G Srinivas                                                                   | Dr.S.Kishore Reddy                                                              | Dr.Vankayalapati<br>Naga Raju                                                             | Dr.S.Kishore Reddy                                                                        | Mr.S.Sagar                                                                                          |

| ECE                                                                             | ECE                                                                             | ECE                                                                                       | ECE                                                                                       | ECE                                                                                                 |

| Journal of Engineering<br>Sciences                                              | Journal of Engineering<br>Sciences                                              | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                         | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                         | Organization Development<br>Journal(ODJ)(SCOPUS<br>INDEX JOURNAL)                                   |

| 2022-23                                                                         | 2022-23                                                                         | 2022-23                                                                                   | 2022-23                                                                                   | 2022-23                                                                                             |

| 0377-9254                                                                       | 0377-9254                                                                       | 0889-6402                                                                                 | 0889-6402                                                                                 | 0889-6402                                                                                           |

| https://jespublication.<br>com/uploads/2023-<br>V14I10059.pdf                   | https://jespublication.<br>com/uploads/2023-<br>V14110059.pdf                   | http://www.journalodj<br>.com/article_view.php<br>?id=50394&ctype=a                       | http://www.journalodj<br>.com/article_view.php<br>?id=50394&ctype=a                       | http://www.journalodj<br>.com/article_view.php<br>?id=50393&ctype=a                                 |

| https://jespublication<br>.com/uploads/2023-<br>V14I10059.pdf                   | https://jespublication<br>.com/uploads/2023-<br>V14I10059.pdf                   | http://www.journalodj.com/article_view.php?id=50394&ctype=a                               | http://www.journalodj.com/article_view.php?id=50394&ctyp_e=a                              | http://www.journalodj.com/article_view.php?id=50393&ctyp_e=a                                        |

| UGC care                                                                        | UGC care                                                                        | SCOPUS                                                                                    | SCOPUS                                                                                    | SCOPUS                                                                                              |

PRINCIPAL

Avanthi Institute of Engg. & Tech

Gunthapally (V), Abdullapumpo (Mg), R.R. Dist.

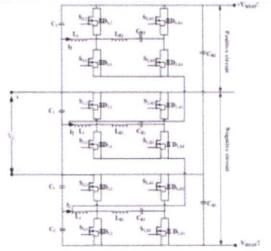

### A NOVEL BI-DIRECTIONAL EV HYBRID ENERGY STORAGE FOR V2G SYSTEM

### BOMMAKANTI MOUNIKA<sup>1</sup>| E.PRASANNA<sup>2</sup>

<sup>1</sup>PG SCHOLAR, Dept of. ELECTRICAL POWER SYSTEM, Avanthi Institute of Engineering and Technology, Ts, India.

<sup>2</sup>ASSISTANT PROFESSOR, Dept of Electrical and Electronics Engineering, Avanthi Institute of Engineering and Technology, Ts, India.

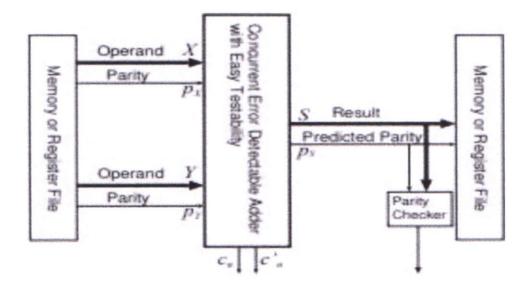

ABSTRACT: This paper gives a switching buck-boost bi-directional converter (SBBBC) for vehicles- to-grid (V2G) machine. The topology can offer a power bidirectional current route for power alternate among the Li-battery/super capacitor (SC) hybrid power garage machine (HESS) of the electrical automobile and the grid. This topology now no longer best has greenbackenhance capability, however additionally has the feature of power management. In this paper, the country-area averaging approach is used to research the steadiness of the topology in enhance and greenback modes. The manage method is given in line with the state of charge (SOC) of the power garage machine to make certain that the output voltage and current are stable. And the Li-battery is charged in constant current (CC) and constant voltage (CV) mode. The voltage and current controllers are designed within side the frequency area primarily based totally on bode plots. Finally, the electric feasibility of the topology, the suitability of the layout controller and manage method are tested with the aid of using simulation.

### **KEYWORDS:**

Vehicles- to-grid (V2G), SBBBC, State of charge, CC, CV.

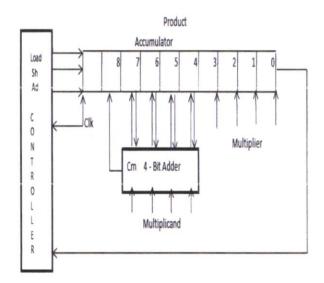

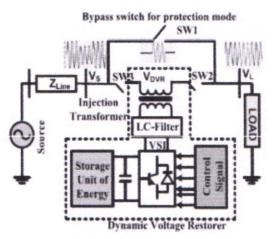

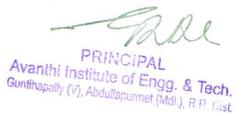

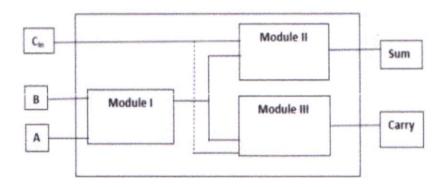

I.INTRODUCTION: Electric vehicles have been widely used because of their cleanliness and low impact on the environment [1]. Li-batteries are of critical importance part in energy storage systems of electric vehicle [2]. Although Li-batteries with high energy densities can provide energy during steady-state enough operation, the power densities of Li-batteries are too low to meet the peak power demand [3], [4]. Combining Li-batteries and supercapacitors (SC) to form a hybrid energy storage system (HESS) can solve the problem. The reason is that SC with higher power densities can provide the transient power required by the load [5][17]. Since output voltage peak of the voltage source inverter is less than the dc-link side voltage, it is necessary to use the dc-dc converter to raise the Li-battery voltage [18]. Figure 1 shows the block diagram of HESS. The SC is directly connected to the inverter, which can increase the dynamic response of the HESS during transient peak power demand, while the Li-battery is connected to the DClink by a bi-directional DC/DC converter [19]. The effect of the bi-directional dc-dc converter in the HESS is to transformer the energy and keeps the dc bus voltage stability. More- over, the converter should

PRINCIPAL

Avanthi Institute of Engg. & Tech. Guntihepally (V), Abdullapurmet (Mdl.), R.R. Dist. provide bi-directional power flow because the energy storage system and the grid require energy exchange [20].

FIGURE 1. The block diagram of HESS.

AHESS topology is mentioned in articles [3] and [5]. In the topology of [3] and [5], the Li-battery can be connected to the SC via a bi-directional dc-dc half-bridge or directly to the DC bus via a diode. This two-stage converter can make full use of the power capacity of the SC but the boost ratio is low. A buck-boost converter for a plug-in hybrid electric vehicle is proposed in paper [21] and [22], respectively. However, the converter mentioned in the paper [21] cannot achieve a bi- directional flow of energy between the grid and the energy storage device. The converter mentioned in the paper [22] has many switching devices, large losses and complicated control. A high voltage gain bi-directional dc-dc converter is given in article [23]. This topology can operate under zero voltage switching conditions and reduces switching and conduction losses. However, this topology has many switching states and the operation is complicated. In [13] and [24], hybrid energy storage systems for electric vehicles based on Z-source inverters (ZSI) and quasi-Z-source inverters (qZSI) were proposed. These two topologies have the boost capability, and provide a bi-directional energy flow path. Moreover, the reliability of the hybrid energy storage system is enhanced due to the characteristics that allow the inverter to shoot-through. These two topologies can increase power density [25]. The control strategies proposed in [13] and [24] is complex, and the topologies have multiple passive components between the SC and the DC bus, which will greatly increase the size of the device.

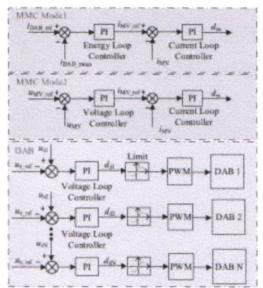

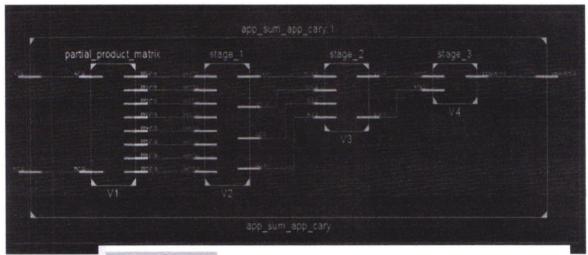

II.PROPOSED SYSTEM: This paper proposes a switching bi-directional buckconverter (SBBBC) appropriate control strategy, which is used in the HESS for vehicles-to-grid (V2G) system. The converter allows shoot-through of two switches of any phase, with antiinterference electromagnetic capability. Meanwhile, since there are three switches in the DC side, the SC and Li-battery can bi-directional fulfill power Furthermore, the small-signal model of the topology is established by state space averaging method and the stability of the system is analyzed. The control strategy is given according to the state of charge (SOC) of the energy storage system and the operating state of the circuit. performance of the proposed converter and control strategy are verified through simulation results.

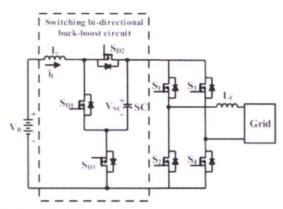

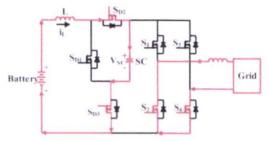

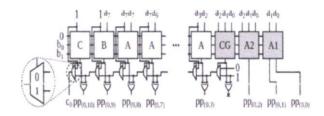

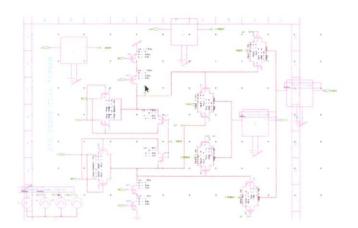

### A. PROPOSED TOPOLOGY

Figure 2 shows the proposed SBBBC with HESS, which consists of five parts: Libattery, switching bi-directional buck-boost circuit, SC, full bridge inverter and gird. The switching bi-directional buck-boost circuit has an inductor, a SC and the additional three switches (SD1, SD2, SD3). Since the gate signals of switches SD2 and SD3 are the same and complementary to the gate signal of switch SD1, one gate signal can control these three additional switches. This

- FARL

PRINCIPAL

Avanthi Institute of Engg. & TechPage No: 51 Gunthapally (V), Abdullapurmet (Mdl.), R.R. Dist.

unique SBBBC network allows the system works on the buck and boost modes, and it can provide bi-directional powerflow.

FIGURE 2. The proposed SBBBC.

TABLE 1. Switch combination and inverter output voltage

| 1 | UAC  | Sui. | So | Son | S | S. | $S_2$ | $S_4$ | state               |

|---|------|------|----|-----|---|----|-------|-------|---------------------|

| 1 | 0    | -0   | 1  | 1   | 0 | 0  | 1     | 1     | zero state          |

| 2 | 0    | 0    | 1  | 1   | 1 | 1  | 0     | 0     | zero state          |

| 3 | -Usc | 0    | 1  | 1   | θ | 1  | 1     | 0     | active state        |

| 4 | Usc  | 0    | 1  | 1   | 1 | 0  | 0     | 1     | active state        |

| 5 | 0    | 1    | 0  | 0:  | 1 | 1  | X     | X     | shoot-through state |

| 6 | 0    | 1    | 0  | 0   | X | X  | 1     | 1     | shoot-through state |

Note:X is 0 or 1.

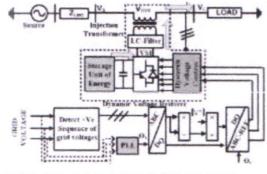

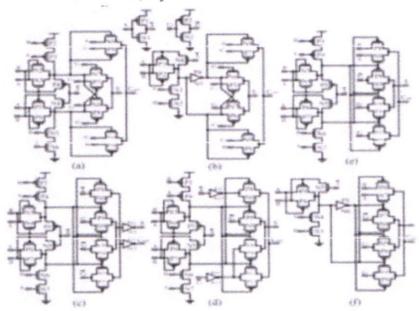

### **B. MODULATION METHOD**

In the proposed converter, there are three switching-states include active state, zero state and shoot-through state respectively, as shown in Table 1. All switches of full bridge inverter are operated in the SPWM mode to modulate output volt- age. The switching bidirectional buck-boost circuit uses the shootthrough duty to achieve buck-boost voltage. The duty cycle is calculated by:

$$\begin{cases} d = m \sin(\theta) \\ d_s = const \\ d_0 = 1 - d - d_s \end{cases}$$

$(d_s \le 1 - d)$  (1)

Where m is the modulation index of the inverter;  $\Theta$  is the vector angle of the output voltage; d, ds, d0 are the duty cycles of the output voltage active state, shoot-through state and zero voltage state, respectively.

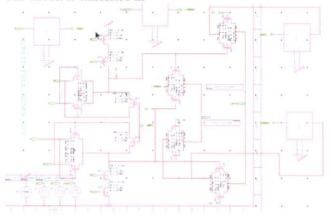

### III. MODELING AND ANALYSIS OF THE PROPOSE CONVERTER

The proposed converter can provide bidirectional power flow among SC, Libattery and grid, as shown in Figure 2. And the converter can work in boost mode and buck mode.

### A. BOOST MODE:

During boost mode, the proposed converter boosts the low Li- battery voltage to high dc-link voltage. There are three work states: zero state, active state and shoot-through state.

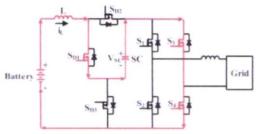

FIGURE 3. Flow path in shoot-through state of boost mode.

### 1) SHOOT-THROUGH STATE

In shoot-through state, the switches SD1 and S3 &S4 (S1 &S2) are turned ON while switches SD2 and SD3 are simultaneously turned OFF, as shown in Figure 3. In this state, the power is transferred from the Libattery and SC to the inductor L. The state equation is given by:

$$\begin{cases} L\frac{di_L}{dt} = -(R_L + R_C)i_L + V_{SC} + V_B \\ C\frac{dV_{SC}}{dt} = -i_L \end{cases}$$

(2)

Where VB is the Li-battery voltage; VSC is the SC voltage; IL is the current through the inductor L; RL and RC are parasitic resistances of the inductor L and SC, respectively.

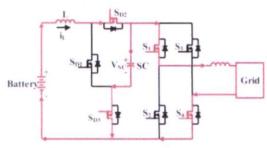

### 2) ACTIVE STATE

In active state, both switches SD2 and SD3 are turned ON while switches SD1 is

simultaneously turned OFF, as shown in Figure 4. In this state, the Li-battery VB and inductor L charge SC and power is transferred from the Li-battery VB and inductor L to the grid. The state equation can be calculated as follows:

$$\begin{cases} L\frac{di_L}{dt} = -(R_L + R_C)i_L - V_{SC} + V_B + R_C i_O \\ C\frac{dV_{SC}}{dt} = i_L - i_O \end{cases}$$

(3)

where  $i_O$  is the output current.

FIGURE 4. Flow path in active state of boost mode.

### 3) ZERO STATE

In zero state, both switches SD2 and SD3 and S1 & S3 (S2 &S4) are turned ON while switches SD1 is simultaneously turned OFF, as shown in Figure 5. The state equation can be calculated as follows.

$$\begin{cases} L \frac{di_L}{dt} = -(R_L + R_C)i_L - V_{SC} + V_B \\ C \frac{dV_{SC}}{dt} = i_L \end{cases}$$

(4)

From equations (2) to (4), due to the average value of the inductor voltage and the capacitor current should be zero in one switching period of Ts, the voltage gain and current gain of the proposed converter in boost mode are as follows [26]:

$$\frac{V_{SC}}{V_B} = \frac{(1 - 2D_{boost})Z_H}{(1 - 2D_{boost})^2 Z_H + (2D_{boost}R_C + R_L)m}$$

(5)

$$i_L = \frac{m}{1 - 2D_{boost}}i_O$$

(6)

FIGURE 5. Flow path in zero state of boost mode.

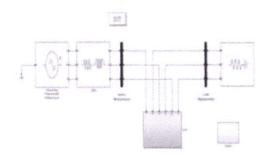

### IV.SIMULATION RESULTS

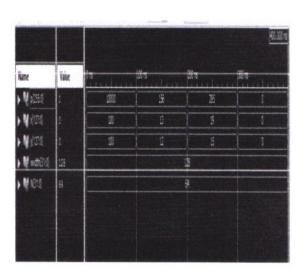

The SBBBC was simulated to verify the feasibility and dynamic performance. The simulation parameters are shown in Table 2.

TABLE 2. Design papameters.

| Parameter                                             | Value | Unit      |

|-------------------------------------------------------|-------|-----------|

| Li-battery voltage V <sub>B</sub>                     | 100   | V         |

| SC voltage Vsc                                        | 200   | V         |

| grid voltage $V_G$                                    | 100   | V         |

| grid voltage frequency                                | 50    | Hz        |

| inductor L                                            | 2     | mH        |

| filter inductor $L_{\ell}$                            | 2     | mH        |

| supercapacitor SC                                     | 2     | F         |

| parallel capacitance of the Li-battery C <sub>1</sub> | 470   | μF        |

| parasitic resistors R <sub>L</sub>                    | 800   | $m\Omega$ |

| parasitic resistors Rc                                | 25    | $m\Omega$ |

| parasitic resistors Re:                               | 51    | $m\Omega$ |

| internal resistance of the Li-battery Rs              | 100   | $m\Omega$ |

| switching frequency $f_i$                             | 5     | kHz       |

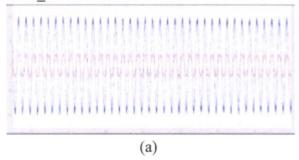

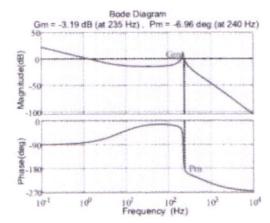

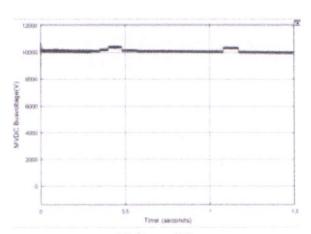

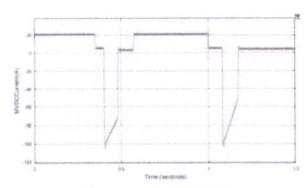

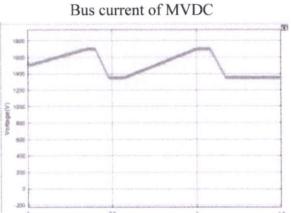

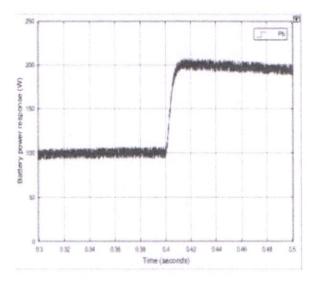

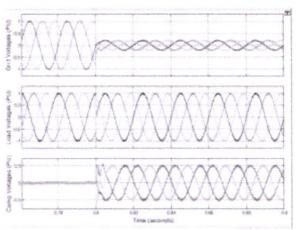

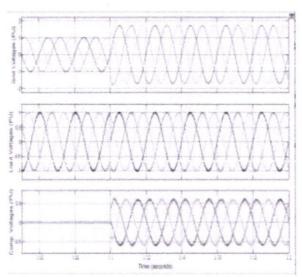

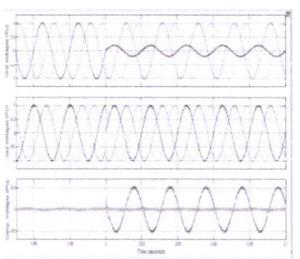

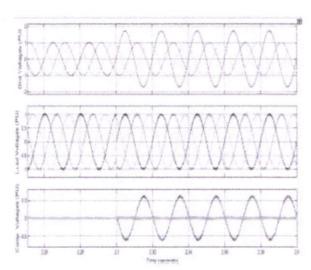

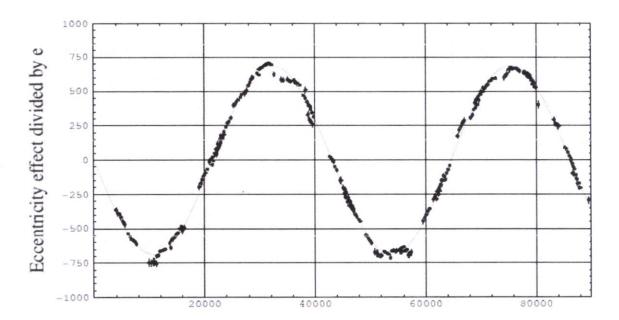

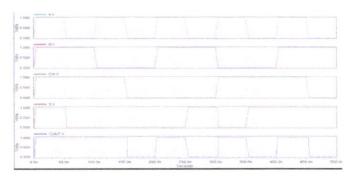

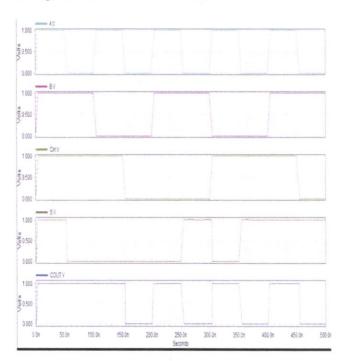

Figure 1 shows the simulation waveforms when the SBBBC is operating in boost mode. To make the grid cur- rent clear, the amplitude of the grid current is amplified 10 times. The current injected into the grid is in phase with the grid voltage to achieve a unit power factor. As shown in Figure 19(b), when the shoot-through duty cycle ds is 0.25, the proposed converter boosts the 100V Li-battery voltage to 200V SC voltage, which meets the voltage gain given by equation (5). At t D 0:5, the reference current IG ref of the grid current controller changes from 4A to 5A. At this time, the Libattery current increases and the output power of the Li-battery increases, this can achieve a fast response of the grid current. The capacitor voltage remains constant and

> Avanthi Institute of Engg. & Techage No: 53 Guntihapally (V), Abdullapumet (Mdl.), R.R. Pist

the energy required by the grid is provided by the Li-battery.

Case 1:V2G Mode

Fig.1. Simulation results of the proposed system. (a) Grid voltage and grid current. (b) Battery discharge voltage and SC voltage. (c) Battery discharge current.

(c)

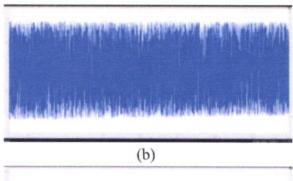

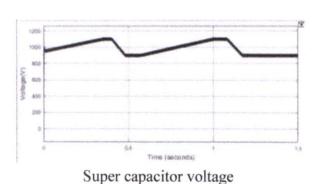

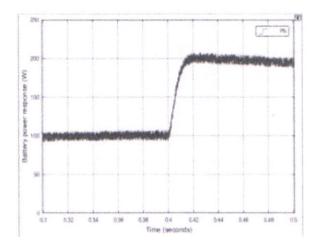

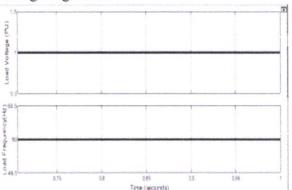

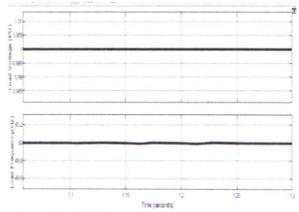

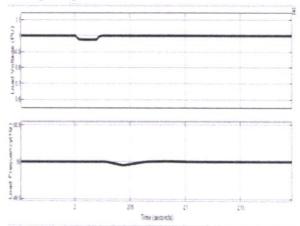

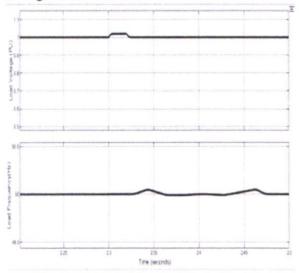

Case 2 G2V Mode

Simulation results of the proposed system.

(a) Grid voltage and grid current. (b) Battery charging current. (c) SC voltage.

### **V.CONCLUSION**

This paper presents a SBBBC for V2G system. The proposed converter not only has high voltage gain and immunity to electromagnetic interference, but provides bidirectional energyflow path. In this paper, different working modes of the SBBBC are discussed in detail and the small signal model of the converter is established. The zero-pole diagram of the system was drawn, the dynamic characteristics of the system were analyzed and its stability was proved. This paper proposes control strategies for V2G and G2V modes, which implement energy management of the HESS. The controller is designed in the frequency domain, so that the controller has good dynamic performance. Finally, the correctness of the theory and the feasibility of the control strategy have been verified through simulations results.

PRINCIPAL

PRINCIPAL Page No: 54

Avanthi Institute of Engg. & Tech.

Gunfihapally (V), Abdullapurmet (Mdl.), R.R. Dist.

### REFERENCES

- [1] F. Naseri, E. Farjah, and T. Ghanbari, "An efcient regenerative braking system based on battery/supercapacitor for electric, hybrid and plug-in hybrid electric vehicles with BLDC motor," IEEE Trans. Veh. Technol., vol. 66, no. 5, pp. 37243738, May 2017.

- [2] S. G. Wirasingha and A. Emadi, "Classication and review of control strategies for plug-in hybrid electric vehicles," IEEE Trans. Veh. Technol., vol. 60, no. 1, pp. 111122, Jan. 2011.

- [3] J. Cao and A. Emadi, "A new battery/ultraCapacitor hybrid energy storage system for electric, hybrid, and plug-in hybrid electric vehi- cles," IEEE Trans. Power Electron., vol. 27, no. 1, pp. 122132, Jan. 2012.